Article originally published on Semiwiki.com, "Viewing the Largest IC Layout Files Quickly"

Wrote by Daniel Payne on 03-10-2020 at 6:00 AM

The old adage, “Time is money”, certainly rings true today for IC designers, so the entire EDA industry has focused on this challenging goal of making tools that help speed up design and physical verification tasks like DRC (Design Rule Checks) and LVS (Layout Versus Schematic). Sure, the big three EDA vendors have adequate IC layout editors, however, they are general-purpose tools not really optimized for loading and viewing the largest IC designs. This creates an opportunity for a focused point tool that excels at quickly reading an IC layout and does chip finishing tasks, which is what Empyrean has done with their Skipper tool.

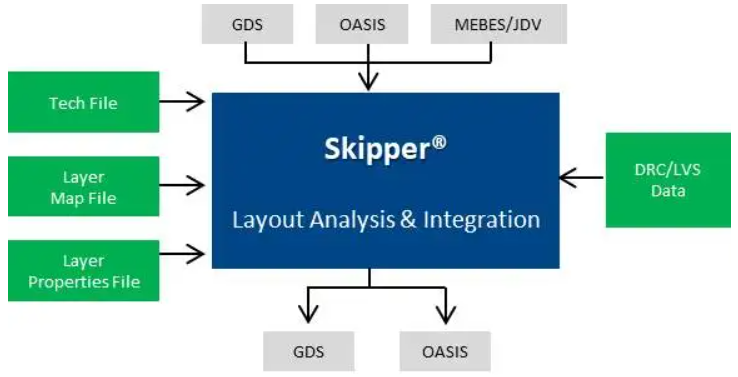

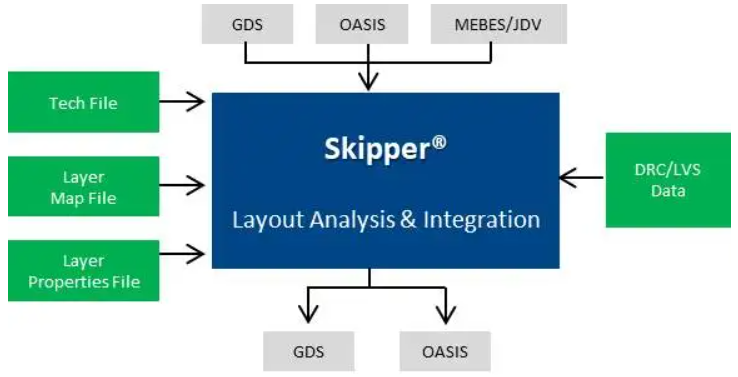

I had a WebEx session last week with Chen Zhao, AE Manager at Empyrean to see what the Skipper tool was all about. Here’s a diagram showing what the input and output file formats are for Skipper:

Let’s say that you have a 200GB OASIS layout file that you need to load and browse, so with a general-purpose IC editor just loading that file would take about 5 hours, however with Skipper the same file loads in just 30 minutes. Now that’s what I call automation. The following six IC design tasks all benefit from a fast tool like Skipper:

- Visualizing IC layout during DRC and LVS debugging.

- Point 2 Point (P2P) resistance analysis.

- Net tracing for VDD, VSS, Clock, etc. to find shorts and opens.

- Merging multiple IP blocks as part of chip finishing.

- Comparing two or more versions of the same layout.

- Focused Ion Beam (FIB) processing for defect analysis and circuit modification.

Using Skipper

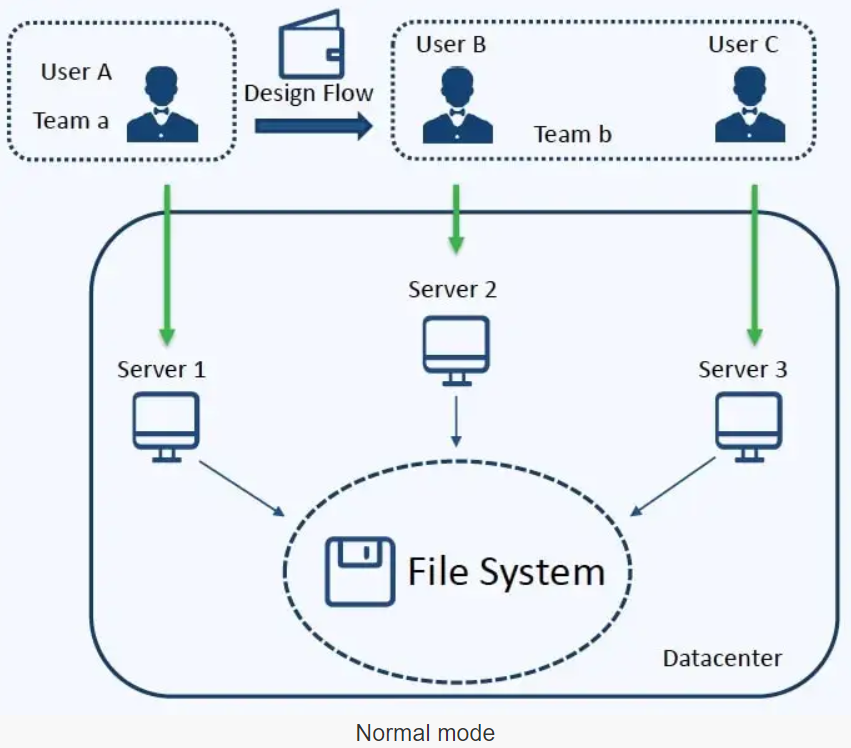

There are three ways to use the Skipper tool, and each method is optimized for certain tasks.

- Normal mode – reads the IC layout file into RAM at speeds up to 1 GB/s, depending on your hard drive being SSD or magnetic.

- Cache mode – reads the IC layout file into RAW leveraging pre-generated index file. It can achieve 2~10X speedup comparing with Normal Mode.

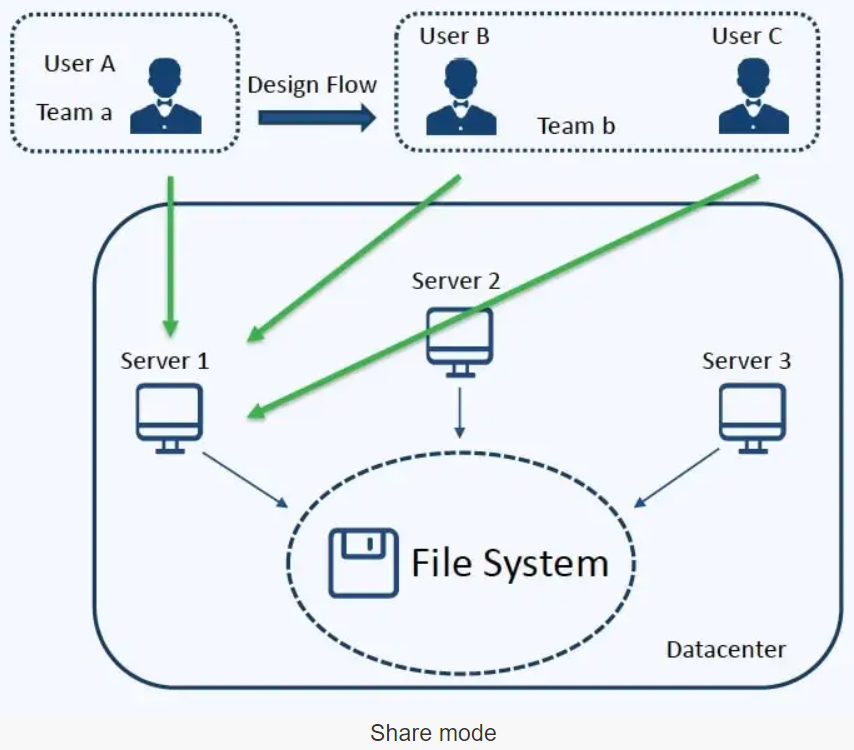

- Share mode – the second user to invoke Skipper on the same machine shares the first RAM image, allowing quickest viewing, typically ready within seconds for a 100+ GB file.

The first two modes sounded like a typical EDA tool, however the share mode was something that I’ve never heard about before, and just watching how fast the IC layout appears is quite exciting.

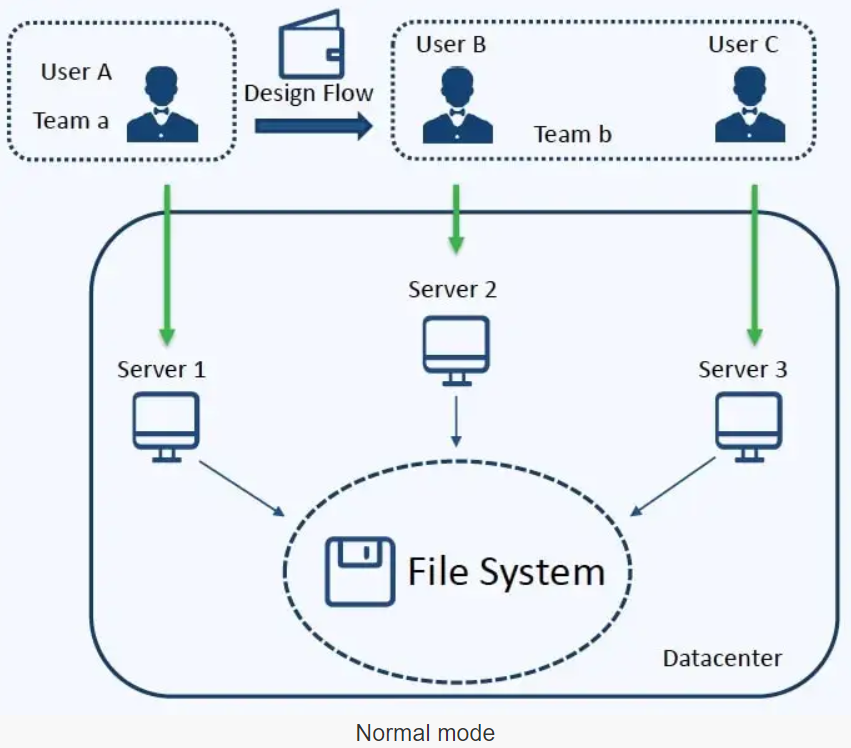

Let’s look at some scenarios for using Skipper starting with Normal mode where each of the following three users independently loads an IC layout, and each has to patiently wait:

With Cache mode User A creates an index file whose size is less than 0.5% of the original layout. User B and C will load the entire IC leveraging the index file with 2~10X faster speed than normal mode.

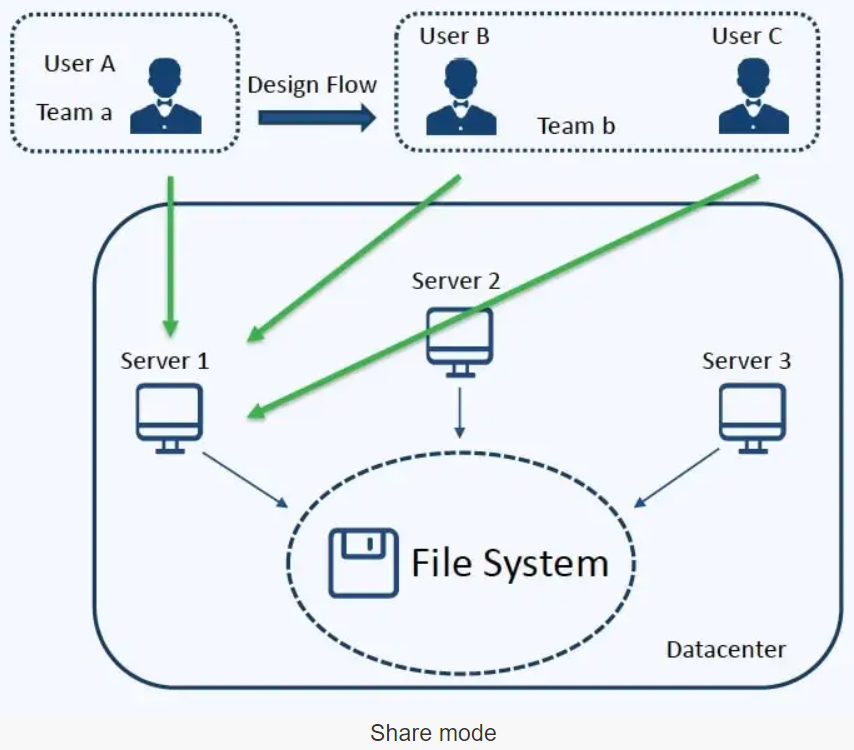

Finally, with Share mode User A is the first to load the IC layout on Server 1, then both users B and C use the same Server 1 with Skipper and share the RAM image, allowing a near-instantaneous viewing experience in just seconds.

To get some speed perspective consider an actual IC design with a 1.6GB OASIS flattened layout, then here are the loading times to start viewing:

- Normal mode: 110 seconds (at 14MB/s reading speed)

- Cache mode: 20 seconds (5.5X faster)

- Share mode: <1 second (100X faster)

Customer Examples

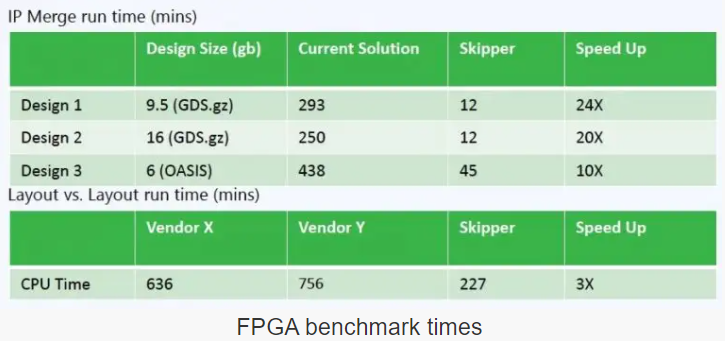

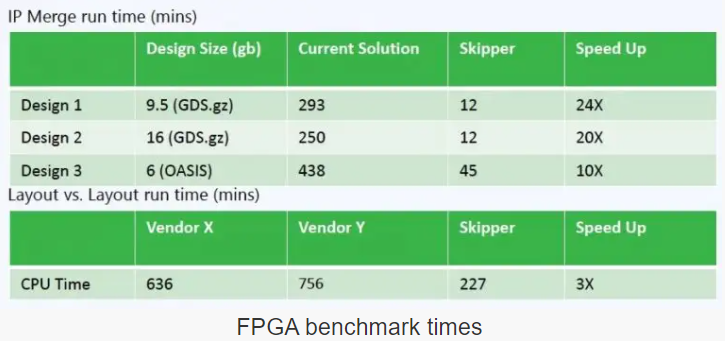

The following two tables compare the speed of Skipper versus another IC layout viewer on an FPGA design, showing improvements between 3X to 24X faster times:

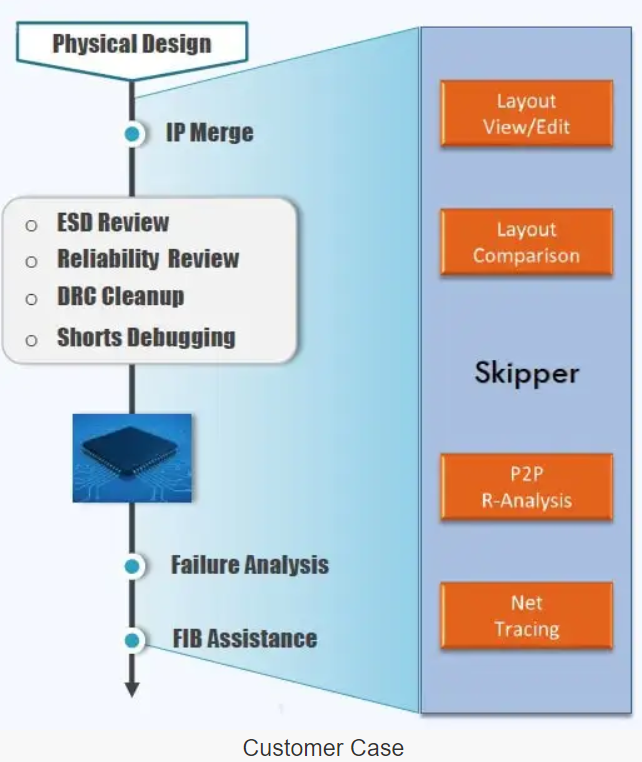

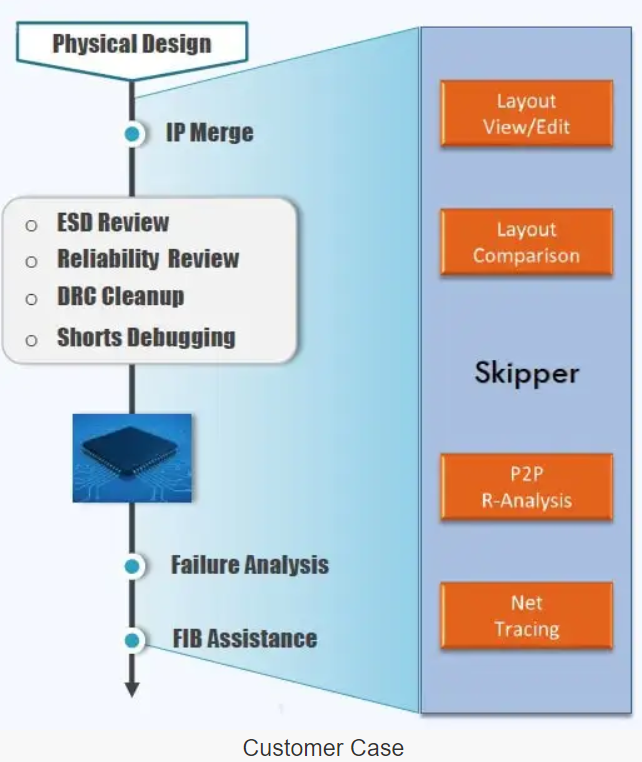

For golden layout signoff using four of the Skipper capabilities a customer found that on designs ranging from 28nm to 7nm benefited from IP merge at 5X faster, and they have used Skipper on 100+ chips so far.

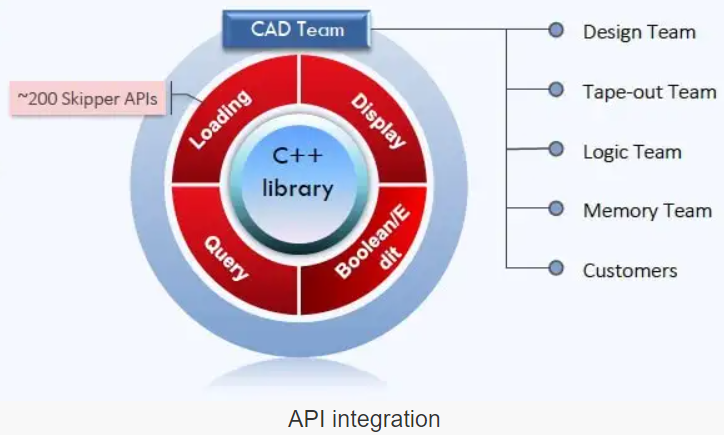

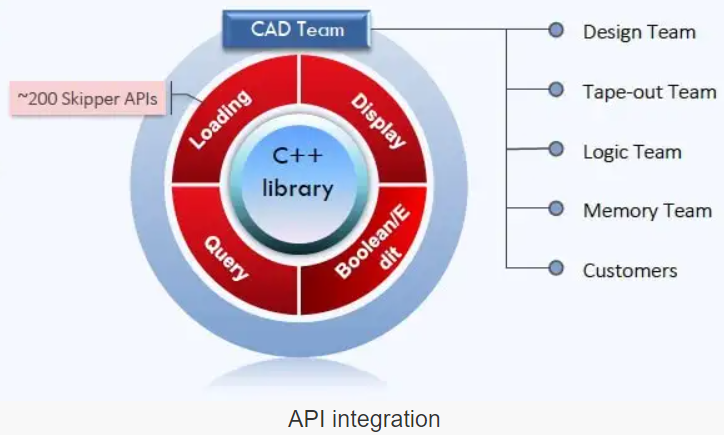

The final customer case involved a CAD group that integrated the Skipper features by using the C++ API in their flow, coding 200+ API features in just 3 months time.

Another way to control Skipper is with Tcl code, so that should keep your CAD guys happy.

Talking about customers, Empyrean has about 300 customers using Skipper, so it’s a proven technology, and a tool category worth taking a closer look at.

TSMC Symposium

If you live in Silicon Valley then consider attending the TSMC Symposium to watch what Skipper can do in real time, and talk with the experts at the Empyrean booth. On Wednesday, April 29th visit the Santa Clara Convention Center.

Summary

There’s a new category of EDA tool for speeding up your LVS/DRC debug times, and LVL checking, where the largest IC designs can be browsed most quickly using a point tool like Skipper, saving you time and improving productivity.

AMS and PMIC Design and Verification Platform

AMS and PMIC Design and Verification Platform

RF IC Design Solution

RF IC Design Solution Digital SoC Design Solution

Digital SoC Design Solution Foundry EDA Solution

Foundry EDA Solution Advanced Packaging Design Solution

Advanced Packaging Design Solution Complete Solution for Flat Panel

Complete Solution for Flat Panel